## EE 330 Lecture 37

#### **Digital Circuits**

Characterization of CMOS Inverter Static CMOS Logic Gates

### Digital Circuit Design

- Hierarchical Design

- Basic Logic Gates

- Properties of Logic Families

- Characterization of CMOS Inverter

- Static CMOS Logic Gates

- Ratio Logic

- Propagation Delay

- Simple analytical models

- Elmore Delay

- Sizing of Gates

- Propagation Delay with Multiple Levels of Logic

- Optimal driving of Large Capacitive Loads

- Power Dissipation in Logic Circuits

- Other Logic Styles

- Array Logic

- Ring Oscillators

### The basic logic gates

It suffices to characterize the inverter of a logic family and then express the performance of other gates in that family in terms of the performance of the inverter.

What characteristics are required and desirable for an inverter to form the basis for a useful logic family?

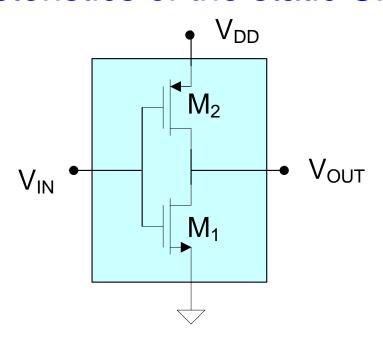

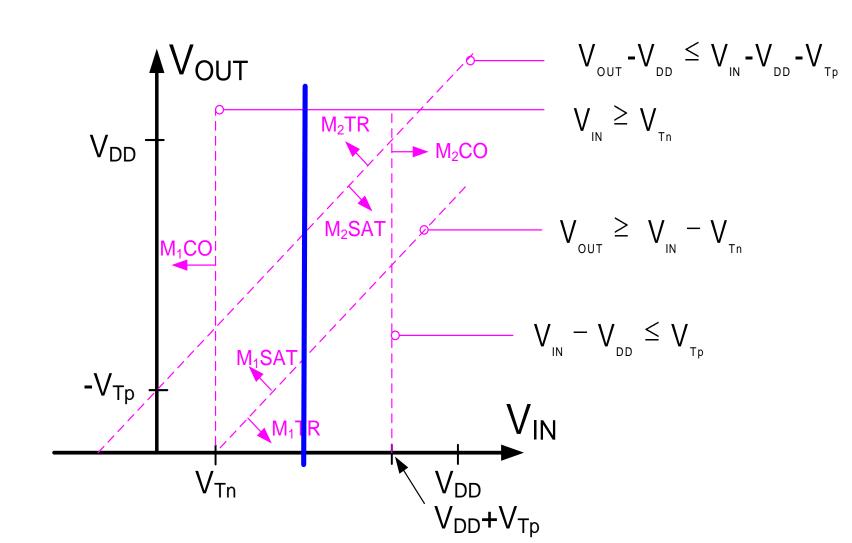

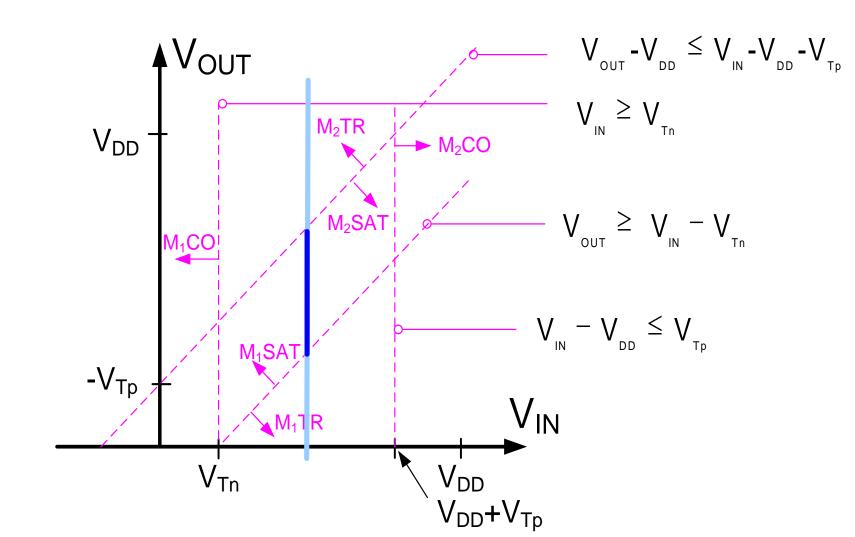

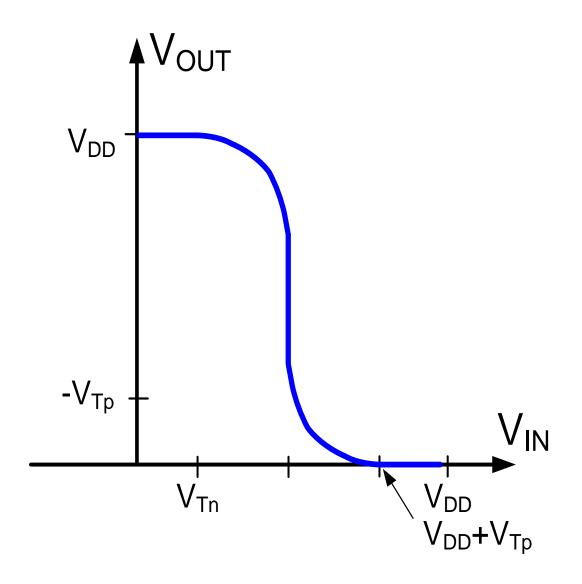

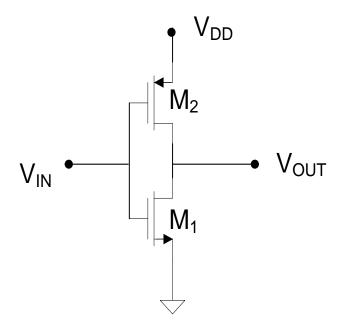

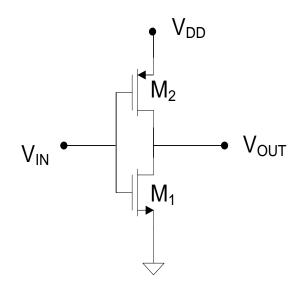

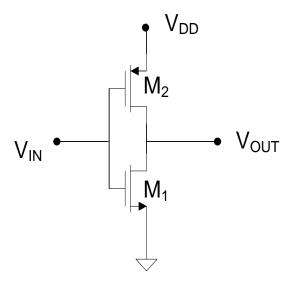

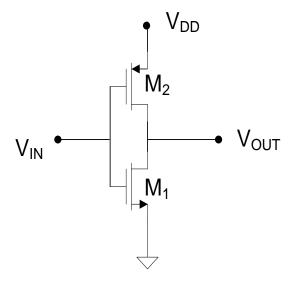

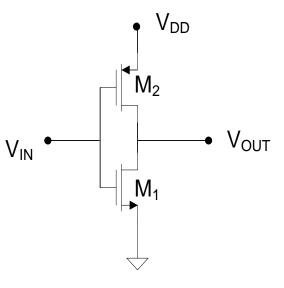

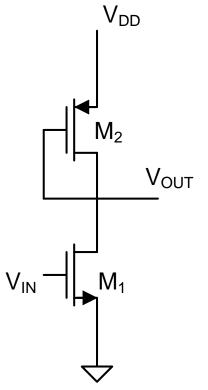

#### Transfer characteristics of the static CMOS inverter

#### Transfer characteristics of the static CMOS inverter

(Neglect λ effects)

Case 3  $M_1$  sat,  $M_2$  sat

$$V_{_{IN}} = \frac{V_{_{Tn}} \sqrt{\frac{\mu_{_{n}}C_{_{OXn}}}{2} \frac{W_{_{1}}}{L_{_{1}}}} + V_{_{DD}} + V_{_{Tp}} \sqrt{\frac{\mu_{_{p}}C_{_{OXp}}}{2} \frac{W_{_{2}}}{L_{_{2}}}}{\sqrt{\frac{\mu_{_{n}}C_{_{OXn}}}{2} \frac{W_{_{1}}}{L_{_{1}}}} + \sqrt{\frac{\mu_{_{p}}C_{_{OXp}}}{2} \frac{W_{_{2}}}{L_{_{2}}}}$$

Since  $C_{ox_n} \cong C_{ox_p} = C_{ox}$  this can be simplified to:

$$V_{_{IN}} = \frac{V_{_{Tn}} \sqrt{\frac{W_{_{1}}}{L_{_{1}}}} + V_{_{DD}} + V_{_{Tp}} \sqrt{\frac{\mu_{_{p}}}{\mu_{_{n}}} \frac{W_{_{2}}}{L_{_{2}}}}}{\sqrt{\frac{W_{_{1}}}{L_{_{1}}}} + \sqrt{\frac{\mu_{_{p}}}{\mu_{_{n}}} \frac{W_{_{2}}}{L_{_{2}}}}}$$

valid for:

$$V_{\text{GS1}} \ge V_{\text{Tn}}$$

$$V_{\text{GS1}} \ge V_{\text{Tn}}$$

$V_{\text{DS1}} \ge V_{\text{GS1}} - V_{\text{Tn}}$   $V_{\text{GS2}} \le V_{\text{Tp}}$   $V_{\text{DS2}} \le V_{\text{GS2}} - V_{\text{T2}}$

$$V_{GS2} \leq V_{Tp}$$

$$V_{DS2} \leq V_{GS2} - V_{T2}$$

thus, valid for:

$$V_{IN} \geq V_{Tn}$$

$$V_{\text{OUT}} \geq V_{\text{IN}} - V_{\text{TI}}$$

$$\bigvee_{IN} - \bigvee_{DD} \leq \bigvee_{TD}$$

$$\bigvee_{\text{IN}} \geq \bigvee_{\text{Tn}} \qquad \bigvee_{\text{OUT}} \geq \bigvee_{\text{IN}} - \bigvee_{\text{Tn}} \qquad \bigvee_{\text{IN}} - \bigvee_{\text{DD}} \leq \bigvee_{\text{Tp}} \qquad \bigvee_{\text{OUT}} - \bigvee_{\text{DD}} \leq \bigvee_{\text{IN}} - \bigvee_{\text{DD}} - \bigvee_{\text{Tp}} - \bigvee_{\text{DD}} - \bigvee_{\text{Tp}} - \bigvee_{\text{DD}} - \bigvee_$$

## Transfer characteristics of the static CMOS inverter (Neglect λ effects)

Case 3  $M_1$  sat,  $M_2$  sat

## Transfer characteristics of the static CMOS inverter (Neglect λ effects)

Case 3  $M_1$  sat,  $M_2$  sat

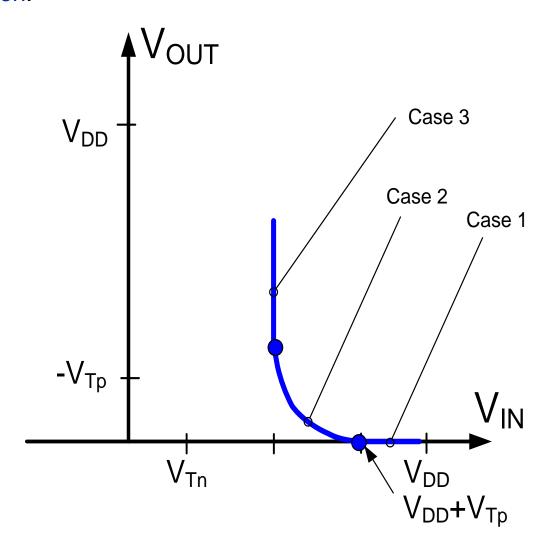

## Review from last time: Transfer characteristics of the static CMOS inverter (Neglect λ effects)

#### Partial solution:

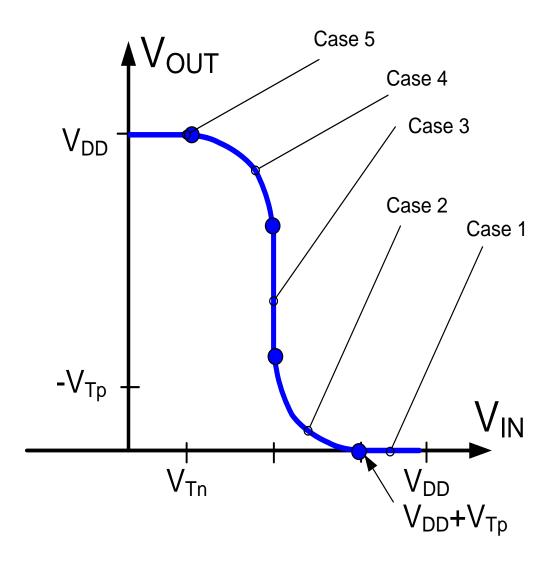

## Transfer characteristics of the static CMOS inverter (Neglect λ effects)

## Transfer characteristics of the static CMOS inverter (Neglect λ effects)

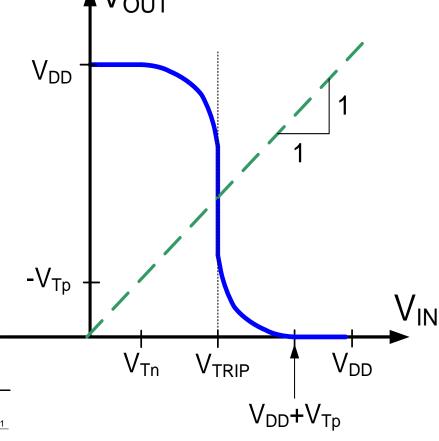

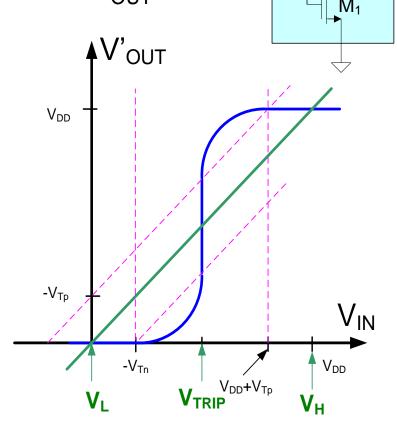

#### Transfer characteristics of the static CMOS inverter

(Neglect  $\lambda$  effects)

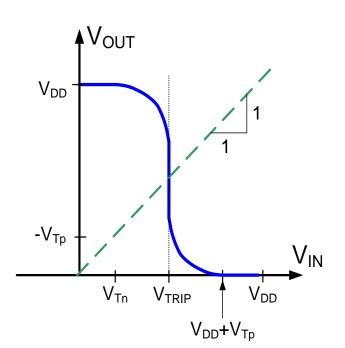

From Case 3 analysis:

$$V_{IN} = \frac{V_{Tn} + V_{DD} + V_{Tp} \sqrt{\frac{\mu_{p}}{\mu_{n}} \frac{W_{2}}{W_{1}} \frac{L_{1}}{L_{2}}}}{1 + \sqrt{\frac{\mu_{p}}{\mu_{n}} \frac{W_{2}}{W_{1}} \frac{L_{1}}{L_{2}}}}$$

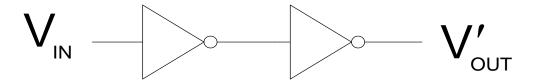

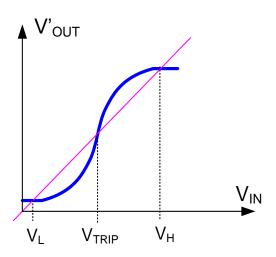

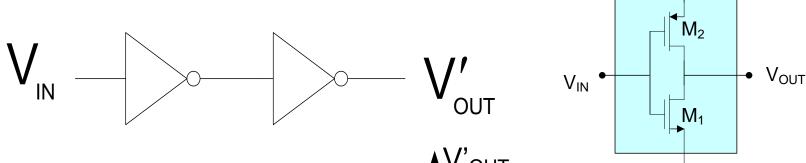

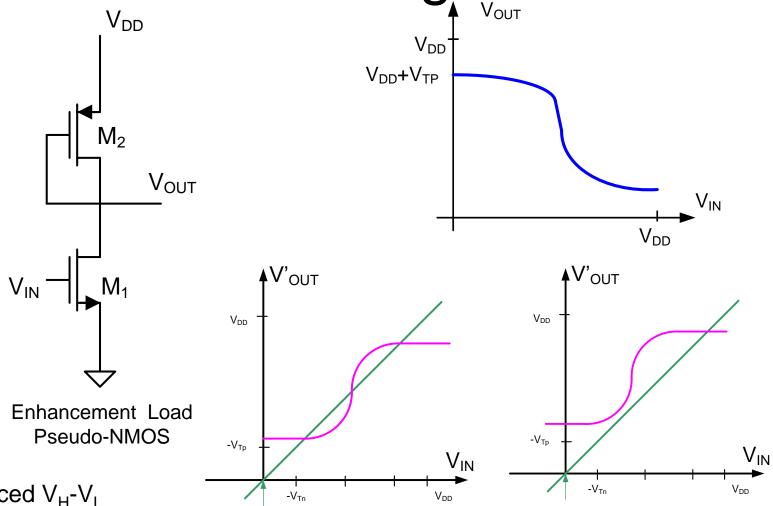

# Inverter Transfer Characteristics of Inverter Pair

What are  $V_H$  and  $V_L$ ?

Find the points on the inverter pair transfer characteristics where  $V_{\text{OUT}}$ '= $V_{\text{IN}}$  and the slope is less than 1

## Inverter Transfer Characteristics of Inverter Pair for THIS Logic Family

$V_H = V_{DD}$  and  $V_I = 0$

Note this is independent of device sizing for THIS logic family !!

$V_{DD}$

#### Sizing of the Basic CMOS Inverter

The characteristic that device sizes do not need to be used to establish  $V_H$  and  $V_L$  logic levels is a major advantage of this type of logic

How should  $M_1$  and  $M_2$  be sized?

How many degrees of freedom are there in the design of the inverter?

How many degrees of freedom are there in the design of the inverter?

$$\{ W_1, W_2, L_1, L_2 \}$$

4 degrees of freedom

But in basic device model and in most performance metrics, W<sub>1</sub>/L<sub>1</sub> and W<sub>2</sub>/L<sub>2</sub> appear as ratios

$$\{ W_1/L_1, W_2/L_2 \}$$

effectively 2 degrees of freedom

$$\{ W_1, W_2, L_1, L_2 \}$$

4 degrees of freedom

Usually pick  $L_1=L_2=L_{min}$

$$\{ W_1/L_1, W_2/L_2 \}$$

effectively 2 degrees of freedom

How are W₁ and W₂ chosen?

Depends upon what performance parameters are most important for a given application!

Usually pick  $L_1=L_2=L_{min}$

$$\{ W_1/L_1, W_2/L_2 \}$$

2 remaining degrees of freedom

One popular sizing strategy:

- 1. Pick  $W_1=W_{MIN}$  to minimize area of  $M_1$

- 2. Pick  $W_2$  to set trip-point at  $V_{DD}/2$

pick

$$L_1=L_2=L_{min}$$

#### One popular sizing strategy:

- 1. Pick W<sub>1</sub>=W<sub>MIN</sub> to minimize area of M<sub>1</sub>

- 2. Pick  $W_2$  to set trip-point at  $V_{DD}/2$

Observe Case 3 provides expression for V<sub>TRIP</sub>

Thus, at the trip point,

$$V_{\text{out}} = V_{\text{in}} = V_{\text{trip}} = \frac{V_{\text{tn}} + V_{\text{dd}} + V_{\text{tp}} \sqrt{\frac{\mu_{\text{p}}}{\mu_{\text{n}}} \frac{W_{\text{2}}}{W_{\text{1}}} \frac{L_{\text{1}}}{L_{\text{2}}}}}{1 + \sqrt{\frac{\mu_{\text{p}}}{\mu_{\text{n}}} \frac{W_{\text{2}}}{W_{\text{1}}} \frac{L_{\text{1}}}{L_{\text{2}}}}}$$

pick

$$L_1=L_2=L_{min}$$

#### One popular sizing strategy:

- 1. Pick  $W_1=W_{MIN}$  to minimize area of  $M_1$

- 2. Pick  $W_2$  to set trip-point at  $V_{DD}/2$

Typically

$$V_{Tn}=0.2V_{DD}$$

,  $|V_{Tp}|=0.2V_{DD}$

$$V_{\text{TRIP}} = \frac{V_{\text{Tn}} + V_{\text{DD}} + V_{\text{Tp}} \sqrt{\frac{\mu_{\text{p}}}{\mu_{\text{n}}} \frac{W_{\text{2}}}{W_{\text{1}}} \frac{L_{\text{1}}}{L_{\text{2}}}}}{1 + \sqrt{\frac{\mu_{\text{p}}}{\mu_{\text{n}}} \frac{W_{\text{2}}}{W_{\text{1}}} \frac{L_{\text{1}}}{L_{\text{2}}}}}$$

$$\frac{V_{DD}}{2} = \frac{0.2V_{DD} + V_{DD} - 0.2V_{DD} \sqrt{\frac{\mu_{p}}{\mu_{n}} \frac{W_{2}}{W_{1}}}}{1 + \sqrt{\frac{\mu_{p}}{\mu_{n}} \frac{W_{2}}{W_{1}}}}$$

Solving this equation for W<sub>2</sub>, obtain

$$W_{2} = W_{1} \left( \frac{\mu_{n}}{\mu_{n}} \right)$$

Other sizing strategies are used as well and will be discussed later!

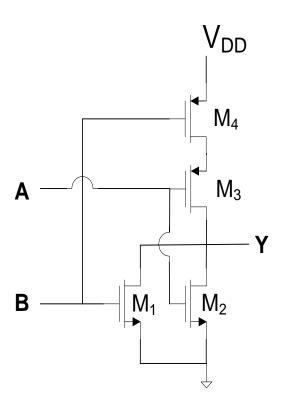

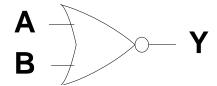

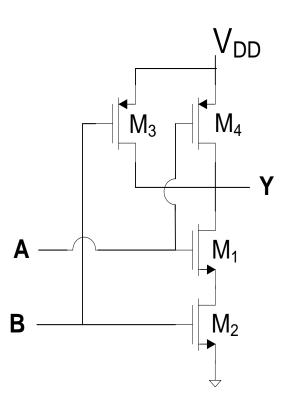

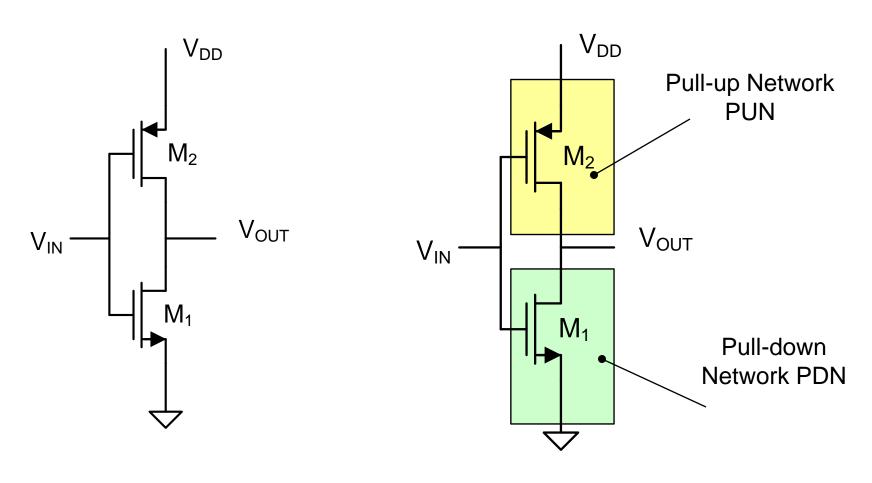

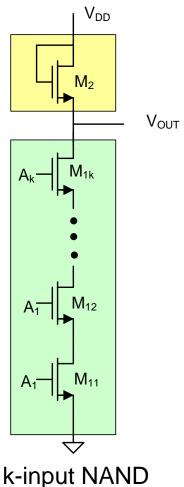

# Extension of Basic CMOS Inverter to Multiple-Input Gates

| Performs as a 2- | input NOR Gate |

|------------------|----------------|

|------------------|----------------|

Can be easily extended to an n-input NOR Gate

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Truth Table

# Extension of Basic CMOS Inverter to Multiple-Input Gates

Can be easily extended to an n-input NAND Gate

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Truth Table

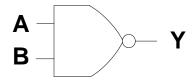

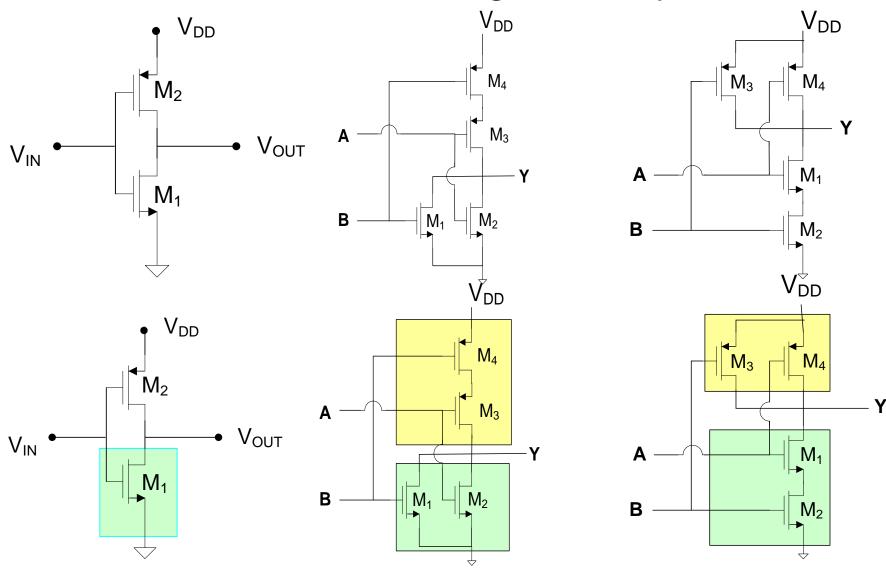

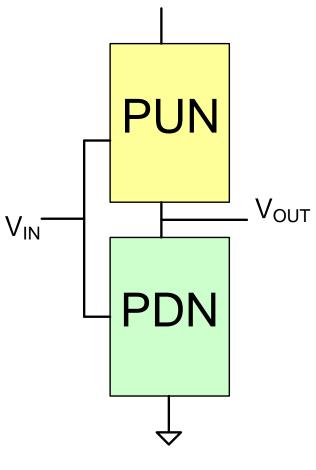

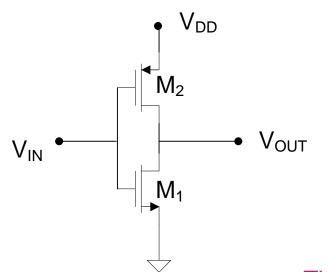

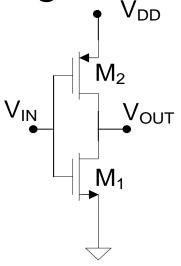

### Static CMOS Logic Family

Observe PUN is p-channel, PDN is n-channel

#### Static CMOS Logic Family

n-channel PDN and p-channel PUN

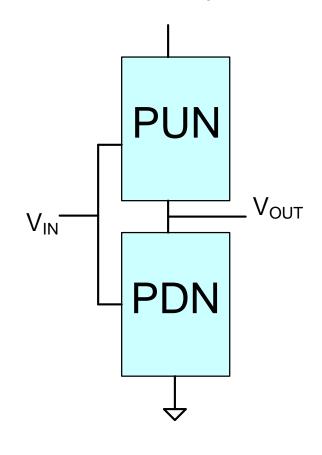

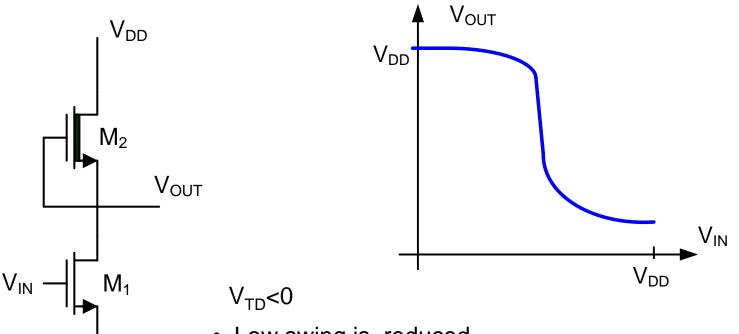

### General Logic Family

p-channel PUN n-channel PDN

Arbitrary PUN and PDN

- High and low swings are reduced

- Response time is slow on LH output transitions

- Static Power Dissipation Large when V<sub>OUT</sub> is low

- Very economical process

- Termed "ratio logic"

- Compact layout (no wells!)

- Multiple-input gates require single transistor for each additional input

- Still useful if many inputs are required (static power does not increase with k

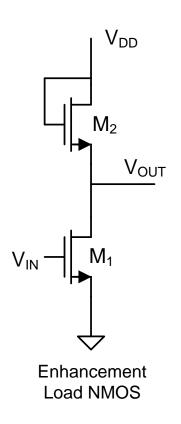

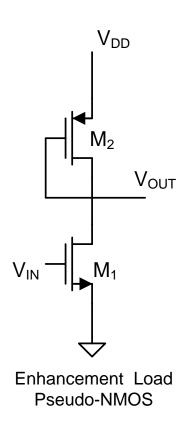

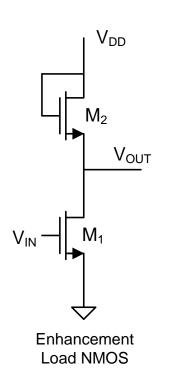

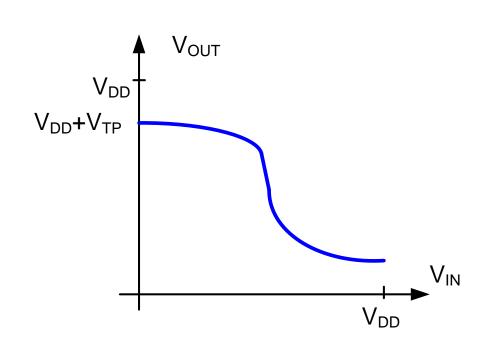

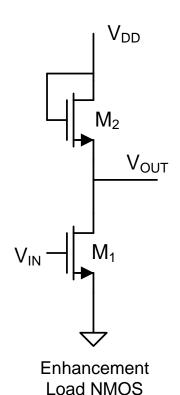

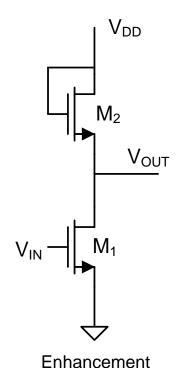

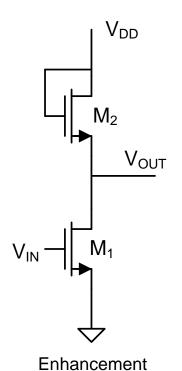

Enhancement Load Pseudo-NMOS

- High and low swings are reduced

- Response time is slow on LH output transitions

- Static Power Dissipation Large when V<sub>OUT</sub> is low

- Termed "ratio" logic

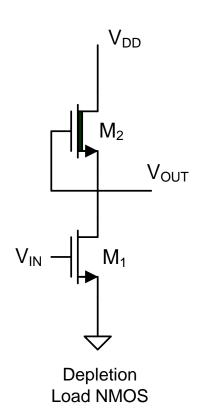

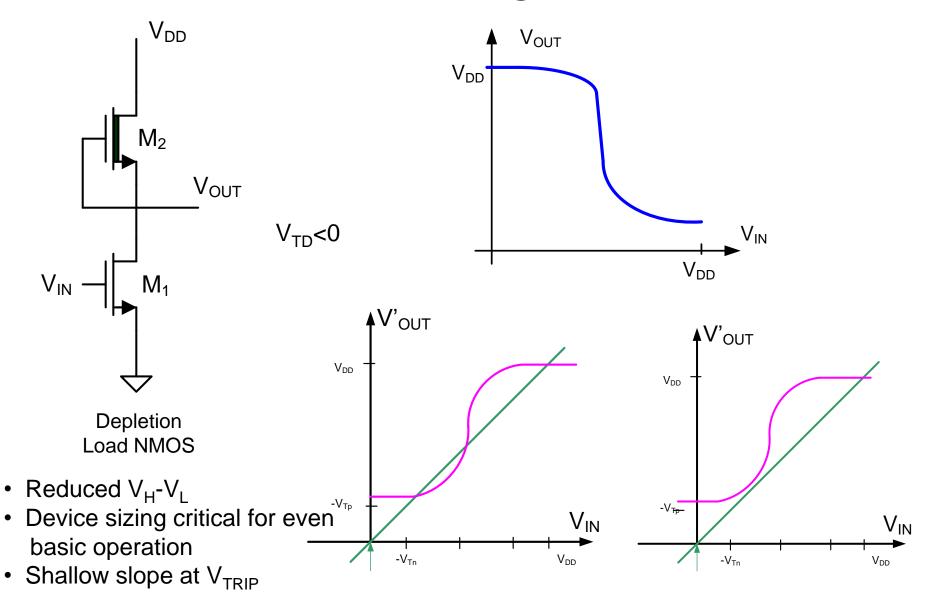

Depletion Load NMOS

- Low swing is reduced

- Static Power Dissipation Large when V<sub>OUT</sub> is low

- Very economical process

- Termed "ratio" logic

- Compact layout (no wells!)

- Dominant MOS logic until about 1985

- Depletion device not available in most processes today

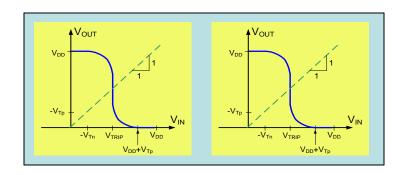

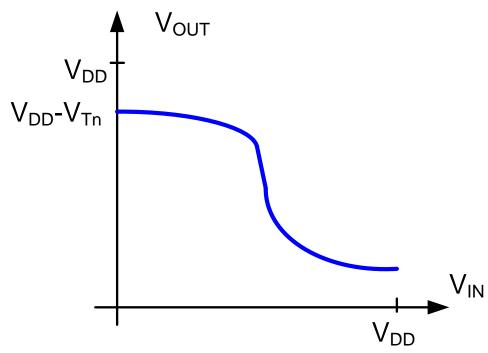

- Reduced V<sub>H</sub>-V<sub>L</sub>

- Device sizing critical for even basic operation

- Shallow slope at V<sub>TRIP</sub>

- Reduced V<sub>H</sub>-V<sub>L</sub>

- Device sizing critical for even basic operation

- Shallow slope at V<sub>TRIP</sub>

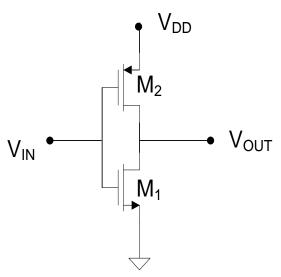

#### Static Power Dissipation in Static CMOS Family

When  $V_{OUT}$  is Low,  $I_{D1}=0$

When  $V_{OUT}$  is High,  $I_{D2}=0$

Thus, P<sub>STATIC</sub>=0

This is a key property of the static CMOS Logic Family and is the major reason Static CMOS Logic is so dominant

It can be shown that this zero static power dissipation property can be preserved if the PUN is comprised of n-channel devices, the PDN is comprised of n-channel devices and they are never both driven into the conducting states at the same time

# Static Power Dissipation in Ratio Logic Families

Example:

Assume  $V_{DD}$ =5V  $V_{T}$ =1V,  $\mu C_{OX}$ =10<sup>-4</sup>A/V<sup>2</sup>,  $W_{1}/L_{1}$ =1 and  $M_{2}$  sized so that  $V_{L}$ = $V_{Tn}$

Observe:

$$V_H = V_{DD} - V_{Tn}$$

If  $V_{IN} = V_H$ ,  $V_{OIIT} = V_I$  so

$$I_{D1} = \frac{\mu C_{OX} W_{1}}{L_{1}} \left( V_{GS1} - V_{T} - \frac{V_{DS1}}{2} \right) V_{DS1}$$

$$I_{D1} = 10^{-4} \left( 5 - 1 - 1 - \frac{1}{2} \right) \cdot 1 = 0.25 \text{mA}$$

$$P_L = (5V)(0.25mA) = 1.25mW$$

# Static Power Dissipation in Ratio Logic Families

Example:

Assume  $V_{DD}\!\!=\!\!5V$   $V_T\!\!=\!\!1V,\,\mu C_{OX}\!=\!\!10^{\text{-}4}\text{A/V}^2,\,W_1\!/L_1\!\!=\!\!1$  and  $M_2$  sized so that  $V_L\!\!=\!\!V_{Tn}$

Load NMOS

$P_L = (5V)(0.25mA) = 1.25mW$

If a circuit has 100,000 gates and half of them are in the  $V_{OUT}=V_{L}$  state, the static power dissipation will be

# Static Power Dissipation in Ratio Logic Families

Example:

Assume  $V_{DD}$ =5V  $V_{T}$ =1V,  $\mu C_{OX}$ =10<sup>-4</sup>A/V<sup>2</sup>,  $W_{1}/L_{1}$ =1 and  $M_{2}$  sized so that  $V_{L}$ = $V_{Tn}$

Load NMOS

$$P_L = (5V)(0.25mA) = 1.25mW$$

If a circuit has 100,000 gates and half of them are in the  $V_{OUT}=V_L$  state, the static power dissipation will be

$$P_{STATIC} = \frac{1}{2} 10^5 \cdot 1.25 \, mW = 62.5W$$

This power dissipation is way too high and would be even larger in circuits with 100 million or more gates – the level of integration common in SoC circuits today

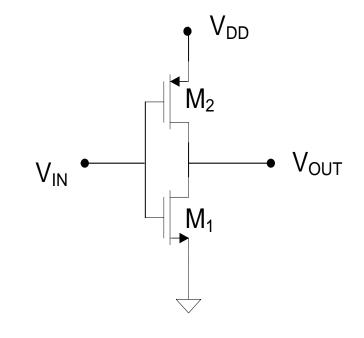

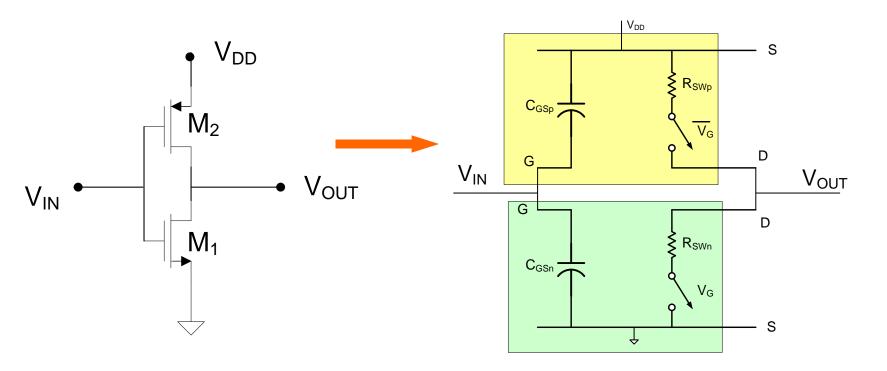

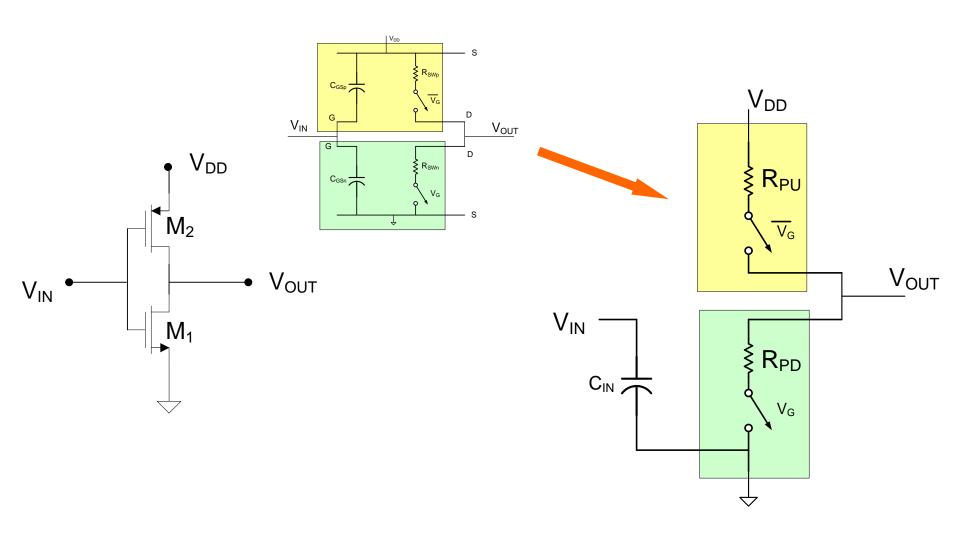

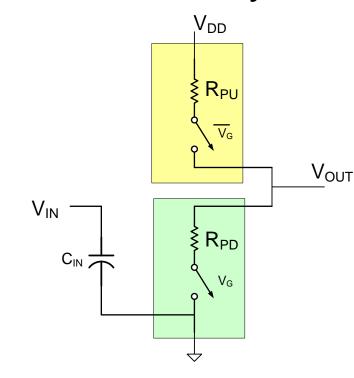

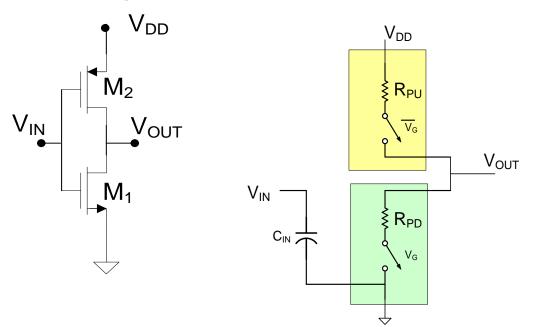

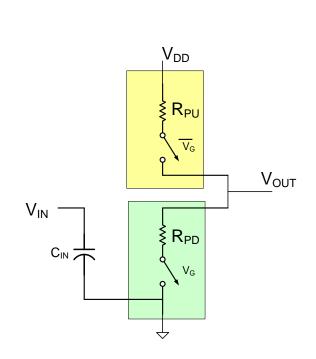

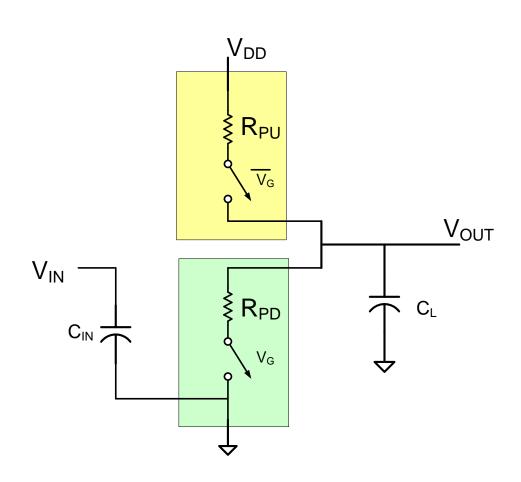

Switch-level model of Static CMOS inverter (neglecting diffusion parasitics)

Switch-level model of Static CMOS inverter (neglecting diffusion parasitics)

Since operating in triode through most of transition:

$$I_{D} \cong \frac{\mu C_{OX} W}{L} \left( V_{GS} - V_{T} - \frac{V_{DS}}{2} \right) V_{DS} \cong \frac{\mu C_{OX} W}{L} \Psi_{GS} - V_{T} \widetilde{Y}_{DS}$$

$$R_{PD} = \frac{L_{1}}{\mu_{n} C_{OX} W_{1} \Psi_{DD} - V_{Tn}}$$

$$I_{D} = \frac{\mu C_{OX} W}{L} \left( V_{GS} - V_{T} - \frac{V_{DS}}{2} \right) V_{DS} \cong \frac{\mu C_{OX} W}{L} \Psi_{GS} - V_{T} \widetilde{Y}_{DS}$$

$$R_{PU} = \frac{L_{2}}{\mu_{p} C_{OX} W_{2} \Psi_{DD} + V_{Tp}}$$

$$C_{IN} = C_{OX} \Psi_{1} L_{1} + W_{2} L_{2}$$

$$R_{PD} = \frac{L_{1}}{\mu_{n}C_{OX}W_{1}\Psi_{DD} - V_{Tn}}$$

$$R_{PU} = \frac{L_2}{\mu_p C_{OX} W_2 \Psi_{DD} + V_{Tp}}$$

$$C_{IN} = C_{OX} \cdot W_1 L_1 + W_2 L_2$$

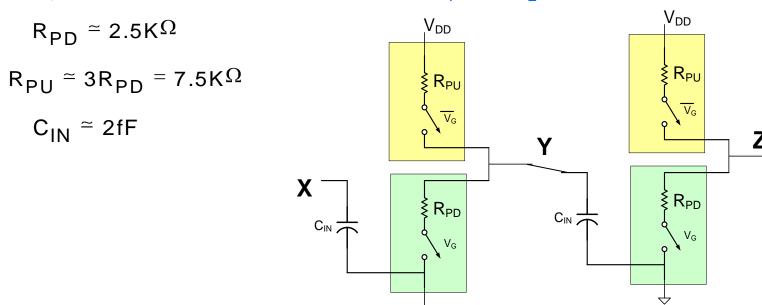

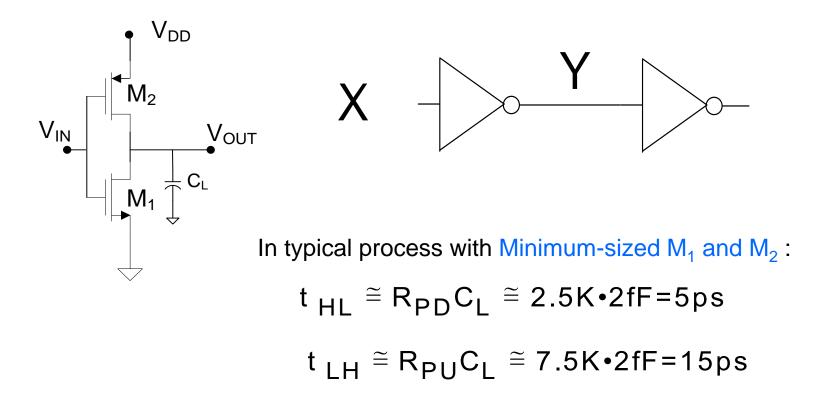

#### Example: Minimum-sized M<sub>1</sub> and M<sub>2</sub>

If  $u_n C_{OX} = 100 \mu AV^{-2}$ ,  $C_{OX} = 4$  fF $\mu^{-2}$ ,  $V_{Tn} = V_{DD}/5$ ,  $V_{TP} = -V_{DD}/5$ ,  $\mu_n/\mu_p = 3$ ,  $L_1 = W_1 = L_{MIN}$ ,  $L_2 = W_2 = L_{MIN}$ ,  $L_{MIN} = 0.5 \mu$  and  $V_{DD} = 5 V$

$$R_{PD} = \frac{1}{10^{-4} \cdot 0.8V_{DD}} = 2.5K \Omega$$

$$C_{IN} = 4 \cdot 10^{-15} \cdot 2L_{MIN}^{2} = 2fF$$

$$R_{PU} = \frac{1}{10^{-4} \cdot \frac{1}{2} \cdot 0.8V_{DD}} = 7.5K \Omega$$

In typical process with Minimum-sized M<sub>1</sub> and M<sub>2</sub>:

$$R_{PD} \simeq 2.5 K\Omega$$

$$R_{PU} \simeq 3R_{PD} = 7.5K\Omega$$

$$C_{IN} \simeq 2fF$$

In typical process with Minimum-sized M<sub>1</sub> and M<sub>2</sub>:

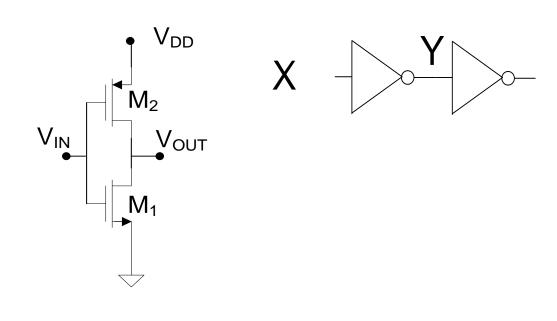

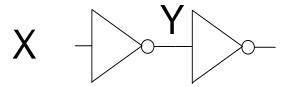

How long does it take for a signal to propagate from x to z?

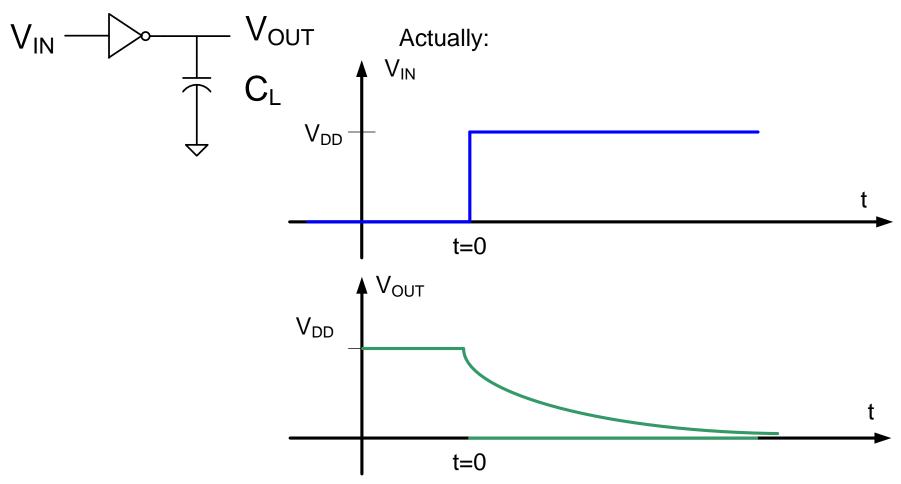

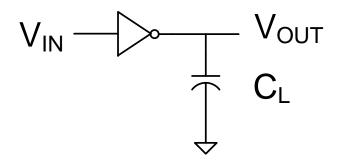

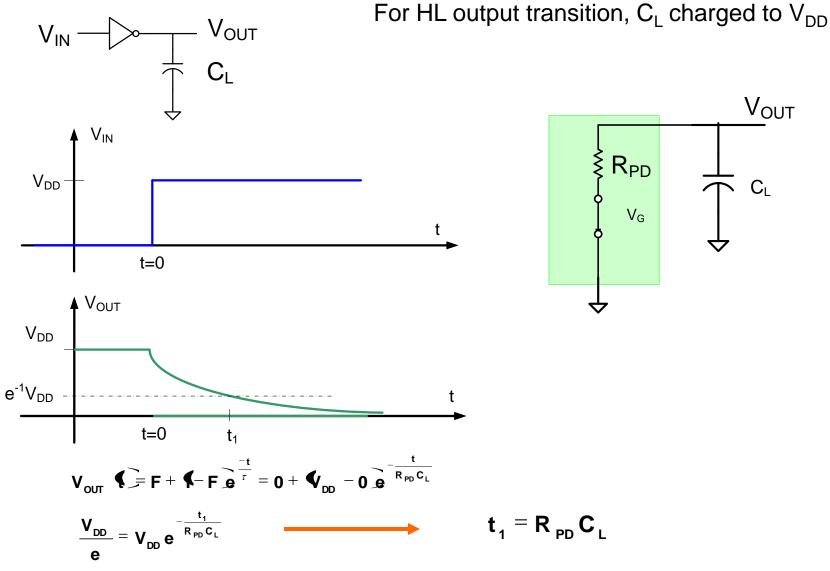

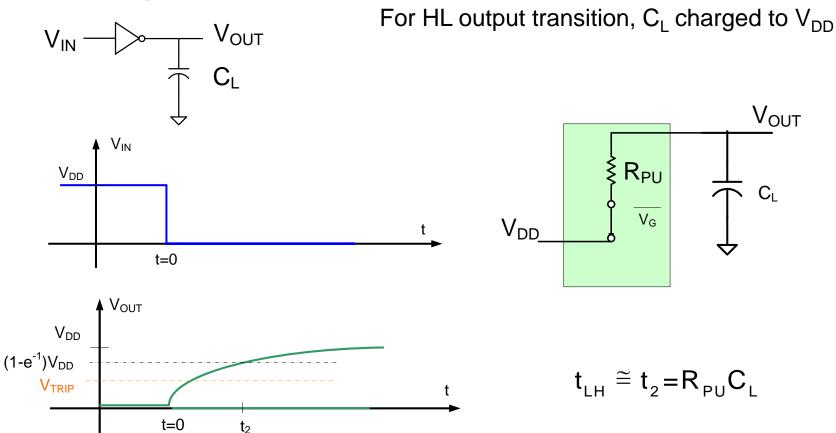

Consider: For HL output transition, C<sub>L</sub> charged to V<sub>DD</sub> Ideally:  $V_{DD}$ t=0  $V_{\text{OUT}}$  $V_{\text{DD}}$

t=0

For HL output transition, C<sub>L</sub> charged to V<sub>DD</sub>

What is the transition time  $t_{HL}$ ?

If  $V_{TRIP}$  is close to  $V_{DD}/2$ ,  $t_{HL}$  is close to  $t_1$

Summary:

$$t_{LH} \cong R_{PU}C_{L}$$

$t_{HL} \cong R_{PD}C_{L}$

Note: LH transition is much slower than HL transition

Defn: The Propagation Delay of a gate is defined to be the sum of  $t_{HL}$  and  $t_{LH}$ , that is,  $t_{PROP} = t_{HL} + t_{LH}$

$$t_{PROP} = t_{HL} + t_{LH} \cong C_L R_{PU} + R_{PD}$$

Propagation delay represents a fundamental limit on the speed a gate can be clocked

#### For basic two-inverter cascade in static CMOS logic

In typical process with minimum-sized  $M_1$  and  $M_2$ :

$$t_{PROP} = t_{HL} + t_{LH} \approx 20 p sec$$

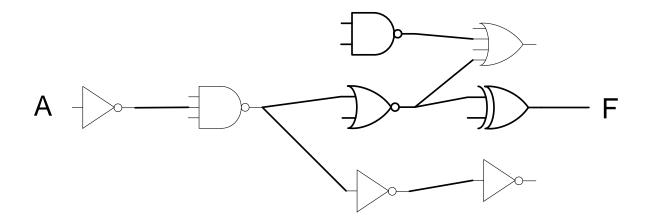

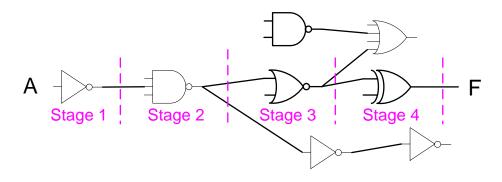

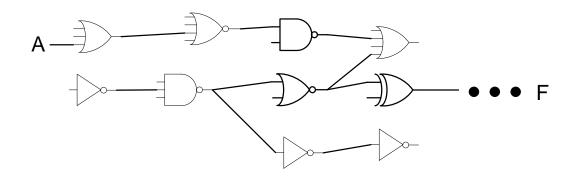

The propagation delay through k levels of logic is approximately the sum of the individual delays in the same path

$$t_{HL} = t_{HL4} + t_{LH3} + t_{HL2} + t_{LH1}$$

$$t_{LH} = t_{LH4} + t_{HL3} + t_{LH2} + t_{HL1}$$

$$t_{PROP} = t_{LH} + t_{HL} = (t_{LH4} + t_{HL3} + t_{LH2} + t_{HL1}) + (t_{HL4} + t_{LH3} + t_{HL2} + t_{LH1})$$

$$t_{PROP} = t_{LH} + t_{HL} = (t_{LH4} + t_{HL4}) + (t_{LH3} + t_{HL3}) + (t_{LH2} + t_{HL2}) + (t_{LH1} + t_{HL1})$$

$$t_{PROP} = t_{PROP4} + t_{PROP3} + t_{PROP2} + t_{PROP1}$$

#### Propagation through k levels of logic

$$t_{HL} \approx t_{HLk} + t_{LH(k-1)} + t_{HL k-2} + \cdots + t_{XY1}$$

$$t_{LH} \approx t_{LHk} + t_{HL(k-1)} + t_{LH k-2} + \cdots + t_{YX1}$$

where x=H and Y=L if k odd and X=L and Y=h if k even

$$t_{PROP} = \sum_{i=1}^{k} t_{PROPk}$$

#### **End of Lecture 37**